Extras din proiect

Capitolul 1: Tema de Proiectare

Sa se proiecteze un sistem de calcul care sa poata efectua operatiile:

- operatii aritmetice (adunare si inmultire)

- operatii logice (sau, inversare)

- operatiile de deplasare: la stanga , la dreapta

- operatii de lucru cu registrii: citire si scriere

- operatii de lucru cu memoria de date

Toate aceste actiuni se vor desfasura prin preluarea unor comenzi dintr-o memorie de program in ritmul unui semnal de ceas. Pe langa proiectarea sistemului propriu-zis se va proiecta si un set de instructiuni care vor genera comenzile din memoria de program. In final pentru a verifica functionarea sistemului se va realiza un program cu instructiunile proiectate care va efectua anumite operatii din cele mentionate.

Din punct de vedere al implementarii, aceasta se face in FPGA Spartan 3, VHDL Schematics.

Sistemul va avea un set de 16 registrii cu dimensiunea de 8 biti fiecare. Dimensiunea memoriei sistemului este de 128K pentru memoria de date si 2K pentru memoria de programe.

Programul de test ce se doreste a fi implementat presupune preluarea a doi operanzi din memoria de date de la adresa 8200h si prelucrarea acestuia prin adunare, dupa care acesta se va depune la adresa 9200h in memoria de date.

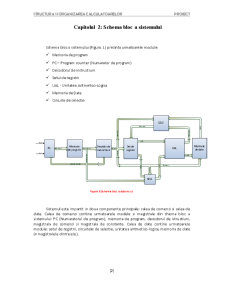

Capitolul 2: Schema bloc a sistemului

Schema bloc a sistemului (Figura. 1) prezinta urmatoarele module:

- Memoria de program

- PC – Program counter (Numarator de program)

- Decodorul de instructiuni

- Setul de registrii

- UAL - Unitatea Aritmetico-Logica

- Memoria de Date

- Circuite de selectie

Figura 1:Schema bloc a sistemului

Sistemul este impartit in doua componente principale: calea de comenzi si calea de date. Calea de comenzi contine urmatoarele module si magistrale din chema bloc a sistemului: PC (Numaratorul de program), memoria de program, decodorul de istructiuni, magistrala de comenzi si magistrala de constante. Calea de date contine urmatoarele module: setul de registrii, circuitele de selectie, unitatea aritmetico-logica, memoria de date (+ magistralele dintre ele).

Calea de comenzi

Numaratorul de program (PC) – Este circuitul care va genera adresa instructiunii care urmeaza sa se execute, aceasta adresa fiind aplicata memoriei de program. Intrarea CLK asigura sincronizarea circuitului, in ritmul acesteia urmand sa fie generate instructiunile. Intrarea de Reset asigura initializarea numaratorului de program. Adresa de salt este intrarea pe care se aplica adresa la care trebuie sa se execute un salt, la executia instructiunilor specifice. Aceasta adresa va fi generata de catre decodorul de instructiuni. Singura iesire a acestui modul este reprezentata de adresa instructiunii.

La realizarea acestui modul se vor folosi urmatoarele circuite: registru paralel-paralel, circuit de incrementare, sumator, circuite de selectie.

Memoria de program este o memorie ROM in care a fost introdus programul ce se va executa. Acest circuit are o singura intrare constituita de adresa instructiunii iar ca iesire va avea codul instructiunii memorat la adresa respectiva. In VHDL memoria de program va fi descrisa ca o memorie RAM distribuita sau ca o memorie Bloc RAM.

Decodorul de instructiuni reprezinta circuitul responsabil cu transformarea instructiunilor in comenzi. Singura intrare este instructiunea care trebuie interpretata si decodificata. Iesirea circuitului este constituita dintr-o magistrala prin care se trimit comenzile catre toate componentele sistemului.

In cazul instructiunilor care folosesc o valoare imediata, se va obtine, din magistrala ce contine instructiunea curenta, si o constanta ce se va transmite catre calea de date (unitatea aritmetico-logica).

Preview document

Conținut arhivă zip

- Structura si organizarea calculatoarelor.docx