Extras din proiect

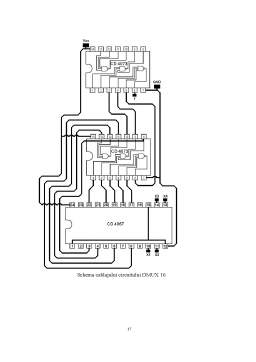

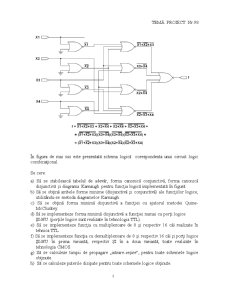

În figura de mai sus este prezentată schema logică corespondenta unui circuit logic combinaţional.

Se cere:

a) Să se stabilească tabelul de adevăr, forma canonică conjunctivă, forma canonică disjunctivă şi diagrama Karnaugh pentru funcţia logică implementată în figură.

b) Să se obţină ambele forme minime (disjunctivă şi conjunctivă) ale funcţiilor logice, utilizându-se metoda diagramelor Karnaugh.

c) Să se obţină forma minimă disjunctivă a funcţiei cu ajutorul metodei Quine-McCluskey.

d) Să se implementeze forma minimă disjunctivă a funcţiei numai cu porţi logice

ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

e) Să se implementeze funcţia cu multiplexoare de 8 şi respectiv 16 căi realizate în tehnica TTL.

f) Să se implementeze funcţia cu demultiplexoare de 8 şi respectiv 16 căi şi porţi logice ŞI-NU în prima variantă, respectiv ŞI în a doua variantă, toate realizate în tehnologia CMOS.

g) Să se calculeze timpii de propagare „intrare-ieşire”, pentru toate schemele logice obţinute.

h) Să se calculeze puterile disipate pentru toate schemele logice obţinute.

i) Să se compare soluţiile de implementare obţinute.

j) Se va face analiza, prin simulare, a tuturor schemelor logice obţinute utilizându-se pachetul de programe OrCAD.

Pe schemele logice obţinute se vor specifica tipul şi gradul de utilizare al fiecărui circuit integrat.

a) Tabelul de adevăr, forma canonică conjunctivă, forma canonică disjunctivă şi diagrama Karnaugh pentru funcţia logică implementată în figură.

;

Termenii sunt redundanţi.

Tabelul de adevăr

Tabelul de adevăr este cea mai completă reprezentare a unei funcţii booleene deoarece pentru fiecare combinaţie posibilă a valorilor argumentelor se indică valoarea funcţiei

Nr

x1 x2 x3 x4

f (x1, x2, x3, x4)

0 0 0 0 0 1

1 0 0 0 1 0

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 1

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 1

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

Preview document

Conținut arhivă zip

- Proiect ASDN.doc