Extras din referat

1. Cresterea de viteza, Legea lui Amdahl. (Speedup & Amdahl Law)

Prin paralelizarea unui program secvential se urmareste in primul rand obtinerea unui timp de executie cat mai mic comparativ cu timpul secvential de executie. Cel mai important criteriu luat in considerare atunci cand se doreste evaluarea performantelor unui program paralel este accelerarea paralela sau cresterea de viteza (speedup) care exprima de cate ori programul paralel este mai rapid fata de varianta secventiala. Accelerarea paralela se calculeaza ca raport intre timpul secvential de executie si timpul de executie paralela:

Valoarea maxima a accelerarii paralele este egala cu numarul de procesoare din sistem. O astfel de valoare poate fi atinsa intr-un sistem ideal in care nu exista costuri de comunicare iar procesoarele sunt incarcate echilibrat.

Legea lui Amdahl reprezinta un model pentru relationarea dintre cresterea de viteza asteptata a unei implementari paralelizate a unui algoritm relativa la o implementare seriala a aceluiasi algoritm, cu precizarea faptului ca dimensiunea problemei va ramane aceeasi cand programul este paralelizat. Legea se refera la cresterea de viteza dobandita de la imbunatatirea unei portiuni f a algoritmului ce are o crestere de viteza standard de S. Legea lui Amdahl ne da cresterea finala de viteza a aplicarii imbunatatirii algoritmului care va fi:

In conformitate cu legea lui Amdahl, chiar si intr -un sistem paralel ideal este foarte dificil de obtinut o accelerare paralela egala cu numarul de procesoare datorita faptului ca in cadrul oricarui program exista o fractie f care nu poate fi paralelizata si care trebuie executata secvential. Restul de (1 - f) pasi de calcul se pot executa in paralel pe procesoarele disponibile in sistem. Astfel, timpul paralel de executie si accelerarea paralela devin:

Atunci cand avem: Din acest motiv, accelerarea maxima care se poate obtine atunci cand o fractie f a programului nu poate fi paralelizata este indiferent de numarul de procesoare din sistem.

Legea lui Amdahl exprima in mod clar necesitatea minimizarii fractiei f ce nu poate fi paralelizata prin stabilirea unei limite superioare a accelerarii paralele.

2. Superbanda de Asamblare (Superpipelining)

Banda de ansamblare (“Pipelining”) este o implementare similara liniei de asamblare, prin utilizarea unor tehnici de suprapunere a fazelor de executie a mai multor instructiuni, ceea ce conduce la cresterea performantelor unitatilor de executie EU (“Execution Unit”) si unitatii de comanda CU (“Command Unit”).

Lucrul in banda de asamblare presupune divizarea unui “task” T in “subtask”-uri T1, , Tk si asignarea “subtask”-urilor la un lant de statii de procesare numite segmente de banda de asamblare. Paralelismul se obtine prin operarea segmentelor simultan. Se pot folosi benzi de asamblare atat la nivelul fluxului de instructiuni, cat si la nivelul fluxului de date, dupa cum se prezinta in figura:

Banda de asamblare poate fi implementata si combinat, atat la nivelul comenzii, cat si la nivelul executiei.

Super banda de ansamblare (superpipelining) permite procesorului sa isi mareasca performanta ruland banda la un clock-rate mai mare. Acest clock-rate este obtinut prin identificarea etapelor care consuma cel mai mult timp si descompunerea acestora in etape mai mici.

Aceasta tehnica nu necesita hardware-ul aditional (precum unitati functionale si fetch) pe care il necesita o arhitectura bazata pe superscalare. Deasemenea, nu necesita tehnologii avansate pentru compilatoare necesare modelului VLIW.

3. Procesoare de tip Superscalar

Utilizarea unitatilor functionale in banda de asamblare confera procesoarelor proprietatea de scalare. In prezent, unitatile functionale in banda de asamblare sunt utilizate, atât de RISC, cât si de CISC, tendinta actuala fiind de superscalare. Superscalarea [81;83;126;127] este o cale de crestere a performantei prin exploatarea paralelismului de granularitate scazuta (“fine-grain”) si executia mai multor instructiuni pe ciclul de ceas.

Executia mai multor operatii pe un ciclu de ceas necesita integrarea de unitati functionale multiple pe acelasi “chip”, care sa permita executia in paralel a „task”-urilor. Problema planificarii “task”-urilor este astfel cruciala in proiectarea procesoarelor moderne. Procesoarele superscalare “veritabile” realizeaza acest lucru prin “hardware” pentru rezolvarea dependentelor de instructiuni. “Hardware”-ul de planificare creste insa geometric cu numarul de unitati functionale si conduce la limitari de implementare.

Superscalarea se realizeaza asadar prin implementarea in unitatea centrala de prelucrare, a unor unitati functionale multiple, fiecare dintre ele fiind organizata in banda de asamblare.

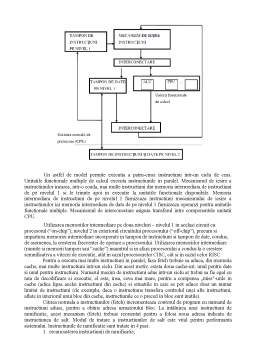

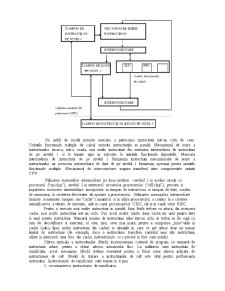

In continuare este prezentat modelul posibil al unui procesor superscalar:

Un astfel de model permite executia a patru-cinci instructiuni intr-un ciclu de ceas. Unitatile functionale multiple de calcul executa instructiunile in paralel. Mecanismul de iesire a instructiunilor incarca, intr-o coada, mai multe instructiuni din memoria intermediara de instructiuni de pe nivelul 1 si le trimite apoi in executie la unitatile functionale disponibile. Memoria intermediara de instructiuni de pe nivelul 1 furnizeaza instructiuni mecanismului de iesire a instructiunilor iar memoria intermediara de date de pe nivelul 1 furnizeaza operanzi pentru unitatile functionale multiple. Mecanismul de interconectare asigura transferul intre componentele unitatii CPU.

Utilizarea memoriilor intermediare pe doua niveluri – nivelul 1 in acelasi circuit cu procesorul (“on-chip”), nivelul 2 in exteriorul circuitului procesorului (“off-chip”), precum si impartirea memoriei intermediare incorporate in tampon de instructiuni si tampon de date, conduc, de asemenea, la cresterea frecventei de operare a procesorului. Utilizarea memoriilor intermediare (numite si memorii tampon sau “cache”) inauntrul si in afara procesorului a condus la o crestere semnificativa a vitezei de executie, atât in cazul procesoarelor CISC, cât si in cazul celor RISC.

Pentru a executa mai multe instructiuni in paralel, faza fetch trebuie sa aduca, din memoria cache, mai multe instructiuni intr-un ciclu. Din acest motiv, exista doua cache-uri: unul pentru date si unul pentru instructiuni. Numarul maxim de instructiuni adus intr-un ciclu ar trebui sa fie egal cu rata de decodificare si executie; el este, insa, ceva mai mare, pentru a compensa „miss"-urile in cache (adica lipsa acelei instructiuni din cache) si situatiile in care se pot aduce doar un numar limitat de instructiuni (de exemplu, daca o instructiune transfera controlul unei alte instructiuni, aflate in interiorul unui bloc din cache, instructiunile ce o preced in bloc sunt inutile).

Citirea normala a instructiunilor (fetch) incrementeaza contorul de program cu numarul de instructiuni aduse, pentru a obtine adresa urmatorului bloc. La intâlnirea unei instructiuni de ramificatie, acest mecanism (fetch) trebuie reorientat pentru a folosi noua adresa indicata de instructiunea de salt. Modul de tratare a instructiunilor de salt este vital pentru performanta sistemului. Instructiunile de ramificatie sunt tratate in 4 pasi:

1. recunoasterea instructiunii de ramificatie;

2. determinarea comportarii instructiunii de ramificatie;

3. calculul adresei de ramificatie;

4. transferul controlului.

1. Recunoasterea instructiunii de ramificatie poate fi realizata mai rapid daca in cache-ul de instructiuni se memoreaza si informatii de decodificare, adica niste biti suplimentari generati de logica de predecodificare si memorati pe masura ce instructiunile sunt aduse in cache.

2. Determinarea comportarii instructiunii de ramificatie este dependenta de instructiunile precedente incomplet executate. Pentru a evita asteptarea terminarii executiei acestora se folosesc metode de predictie a comportarii instructiunilor de salt. Unele predictoare folosesc informatia statica, prezenta in codul binar: unele instructiuni de salt determina transferul controlului mai des decât altele, cum este cazul instructiunilor de ciclare (compilatoarele pot introduce informatii despre probabilitatea de efectuare a salturilor, pe baza analizei programului in limbaj de nivel inalt). Majoritatea predictoarelor folosesc informatia dinamica, disponibila in momentul executiei programului; aceasta se refera la comportarea anterioara a instructiunii de salt (curenta, si eventual a celor precedente) si este pastrata in tabele de predictie sau chiar in blocurile din cache care contin instructiunea de salt. Aceste tabele de predictie sunt organizate intr-o maniera asemanatoare memoriilor cache, fiind accesibile cu adresa instructiunii de salt care trebuie executata anticipat. Istoria comportarii saltului este inregistrata folosind contoare, ce sunt incrementate la executia saltului, respectiv decrementate la neindeplinirea conditiei de salt. Valoarea acestui contor reflecta comportarea dominanta a instructiunii de salt. Se utilizeaza, mai nou, scheme de predictie corelate, pe baza a doua informatii: istoria saltului curent si, respectiv, situarea acestuia in context, pe baza salturilor anterioare. Procesul de citire a instructiunilor (fetch) continua pe baza pre-dictiei, pâna in momentul in care conditia de salt poate fi evaluata pe baza datelor concrete. Acum informatia de predictie poate fi actualizata. Daca predictia nu a fost corecta, mecanismul de citire (fetch) trebuie reorientat de la o noua adresa, acum cunoscuta cu precizie. in plus, trebuie inlaturate si efectele produse de executia speculativa a instructiunilor aduse pe baza predictiei (in acest caz, eronate).

Preview document

Conținut arhivă zip

- Procesoare Evoluate.doc