Extras din curs

Suntem gata sa implementam procesorul MIPS:

Cap 2: performanta unei masini e determinata de 3 factori cheie:

nr de instructiuni, durata ciclului de ceas, nr cicli de ceas pe instructiune (CPI).

Cap 3 si 4: determina nr de instr necesare pt a scrie un program.

Cap 5: Arata ca durata ciclului de ceas si nr de cicli de ceas pe instr este determinat de implementarea procesorului.

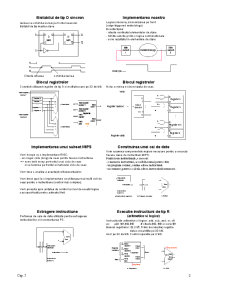

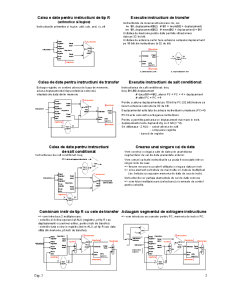

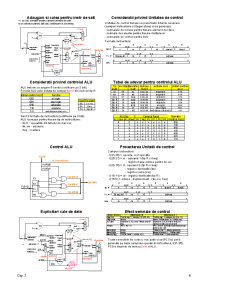

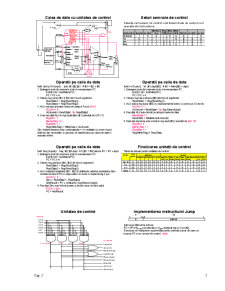

Vom prezenta 2 implementari diferite ale cailor de date si unitatii de control pentru un subset de instr MIPS:

- instr de transfer: lw, sw

- instr aritmetice si logice: add, sub, and, or, slt

- instr salt conditinat si salt: beq, j

Executia unei instructiuni se face in mai multi pasi. Toate instructiunile au primii 2 pasi identici:

1. Utilizeaza program counter (PC) pentru a asigura adresa de memorie de la care se extrage codul instructiunii

2. Citeste unul sau doua registre indicate de campul instr

Utilizeaza instructiunea pentru a decide exact e trebuie sa faca.

Toate instr utilizeaza ALU dupa citirea registrelor:

- instr de transfer: pt calcul adresa memorie

- instr aritmetice si logice: pentru executia operatiei

- instr de salt: pentru comparatie

Dupa ce utilizeaza ALU:

- instr de transfer: acces la memorie pentru citire/scriere

- instr aritmetice si logice: scrie rezultatul intr-un registru

- instr de salt: scriu noua adresa in PC pentru salt

Doua tipuri de elemente functionale:

- combinatinale - care opereaza asupra valorilor datelor

(iesirile depind strict de intrarile curente), ex: ALU

- secventiale - care memoreaza stari (elemente de stare),

ex: memoriile de instructiuni si date, registrele (bistabile)

Preview document

Conținut arhivă zip

- Procesorul - Caile de Date si Unitatea de Control

- Cursarh5.doc

- CursArhCap5-1.ppt

- CursArhCap5-2.ppt

- CursArhCap5-3.ppt