Extras din curs

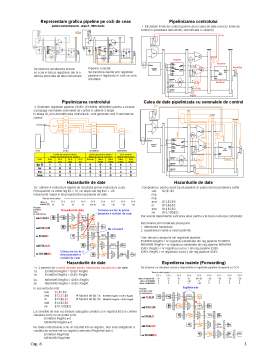

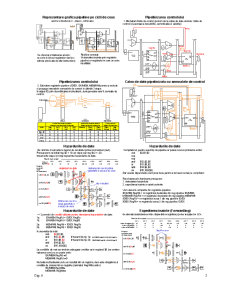

Def: = o tehnica de implementare in care mai multe instructiuni sunt suprapuse in executie.

Introdusa in 1964 prin calculatoarele IBM 7030 si CDC 6600 - suprapunerea fazelor de extragere, decodificare, executie si salvare rezultat.

Reintrodusa incepand cu 1985 de microprocesoarele RISC.

Pipelining-ul este cheia vitezei procesoarelor actuale.

Viteza se obtine prin cresterea ratei de executie a instructiunilor.

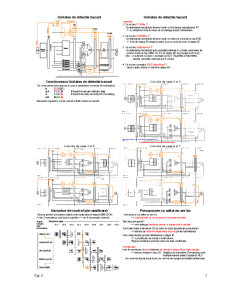

O instructiune MIPS se executa in 5 pasi:

1. Extragere instr din memorie si incrementare PC

2. Decodificare instructiune si extragere registru

3. Executie operatie sau calcul adresa memorie

4. Acces operand in memorie

5. Scrie rezultat intr-un registru

Duratele operatiilor sunt:

Ce face pipelining-ul usor:

- toate instructiunile au aceeasi lungime

- numar mic de formate de instructiuni

- operanzii memorie apar numai in instructiuni de incarcare si salvare

Sunt caracteristici pentru procesoarele RISC.

80x86 au instr de 1-17 octeti, nr mare de moduri de adresare,

instr cu operanzi in memorie => pipelining-ul e o mare provocare.

Ce face pipelining-ul greu:

- hazardurile structurale (conflicte generate de partajarea resurselor,

ex: registre, memorie)

- hazardurile de control (probleme generate de instructiunile de salt,

ce se intampla cu instructiunile care sunt deja in pipeline?)

- hazardurile de date (o instructiune ce foloseste rezultatul instructiunii

anterioare)

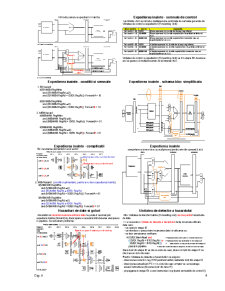

Vom construi un pipeline simplu si vom examina aceste probleme si modalitatile de rezolvare a lor.

Vom vorbi despre procesoarele moderne, despre arhitecturile superscalare, despre executia out-of-order (ne-ordonata) si terminarea in-order (in ordine).

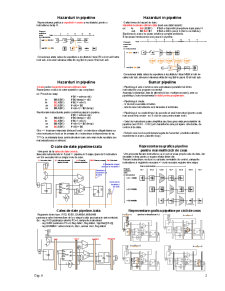

Hazard = eveniment in pipeline care face ca instructiunea urmatoare sa nu poata fi executata in urmatorul ciclu de ceas.

1. Hazardul structural

- apare daca hardware-ul nu suporta unele combinatii de instructiuni in acelasi ciclu de ceas (urmare a unui conflict de acces la o resursa).

Ex: daca avem o memorie comuna pentru date si instructiuni, instructiunea 4 nu va putea fi incarcata.

Solutie: multiplicarea resurselor (memorii separate pentru date si instructiuni)

Preview document

Conținut arhivă zip

- Procesorul - Cresterea Performantelor prin Pipeline

- CursArhCap6-1.ppt

- CursArhCap6-2.ppt

- CursArhCap6-3.ppt

- CursArhCap6.doc