Extras din notiță

1. Memoria CACHE: dpdv al utilizatorului final exista 2 caracteristici importante ale memoriei: 1) capacitatea si 2) performanta. Cei mai importanti parametrii care determina performanta sunt: a) timpul de acces (access time), b) durata unui ciclu de ceas (memory cycle time), c) rata de transfer (transfer rate). A) in cazul memoriilor cu acces aleator, timpul de acces reprezinta timpul necesar pentru preluarea unei date din memorie; pentru memoriile cu acces secvential sau direct reprezinta timpul necesar mecanismului de adresare pentru a ajunge la locatia de memorie dorita + timpul necesar preluarii datelor. B) durata unui ciclu de ceas reprezinta timpul de acces + acea durata necesara sistemului de adresare pentru a fi pregatit sa serveasca o noua cerere. La acest timp se poate aduna in unele cazuri si timpul necesar sistemului de regenerare a datelor. C) rata de transfer reprezinta viteza cu care datele sunt scrise sau citite din unitatea de memorie. Pentru memoria cu acces aleator rata de transfer este egala cu inversul duratei unui ciclu de ceas de memorie.

3. Consistenta datelor in mem. CACHE: Pentru a putea asigura consistenta datelor (integritatea) se foloseste un protocol numit MESI (modified/exclusive shared/invalid). Acesta a fost proiectat pentru a asigura consistenta datelor in sistemele multi procesor care folosesc partajat un singur sistem de memorie, dar a fost implementat cu succes si in cazul uP Pentium II. Fiecare linie din memoria CACHE are asociati 2 biti de stare care pot indica 4 stari: a) modify: semnaleaza faptul ca datele din memoria CACHE sunt diferite decat cele din memoria principala si sunt disponibile numai in CACHE; b) exclusive: indica faptul ca datele din respectiva linie sunt prezente sub aceeasi forma si in memoria principala dar nu sunt disponibile in alte memorii cache; c) shared: datele din linia respectiva sunt prezente si in memoria principala si in memoria CACHE; d) invalid: linia respectiva nu contine date valide. Urmeaza schema.

4. RAM dinamic: cea mai mare problema a arhitecturilor realizate cu uP moderne este viteza de transfer a datelor din memoria principala. Incepand cu anul 1970 pana la inceputul anilor 1990 structura memoriilor DRAM s-a schimbat extrem de putin sau deloc. Cresterea frecventei de ceas a uP a stimulat cercetarile in directia gasirii unor solutii de scadere a timpului de acces la date. Prima idee si cea mai des utilizata a fost inserarea unor memorii tampon SRAM (static) intre uP si DRAM.

5. Enhanced DRAM (EDRAM): a fost dezvoltat de firma RAMTRON in 1994 ideea constand in integrarea unei memorii SRAM la nivelul fiecarei chip de memorie. Memoria SRAM stocheaza un intreg rand care consta din 2048 de biti in 512 felii (slices) de 4 biti. Un comparator stocheaza cei 11 biti ai ultimei adrese selectate. Daca un urmator acces are loc in acelasi rand datele sunt trimise din memoria SRAM. Mai sunt si alte imbunatatiri aduse de aceasta arhitectura si anume: 1) operatia de refresh se face in paralel cu citirea datelor din mem CACHE, 2) calea de citire de la CACHE spre buferele de I/O este independenta de calea de scriere ceea ce inseamna ca o noua operatie de citire poate fi initiata in paralel cu finalizarea unei operatii de scriere. Figura!

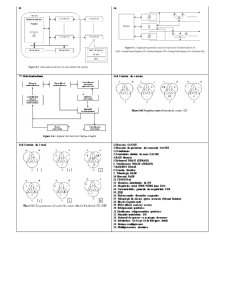

8. Corectia erorilor. O memorie semiconductoare nu poate functiona fara a genera erori. Erorilor pot fi de natura hardware sau software: a) hardware: e generata de cele mai multe ori de un defect fizic al celulei de memorie (fie nu memoreaza informatia dorita, fie celula comuta aleator intre 0L si 1L fara a tine cont de continutul incarcat). Defectele hardware se produc din cauza manevrarilor gresite, a utilizarilor neadecvate, descarcari electrostatice etc., si mult mai rar din cauza defectelor de fabricatie. Defectele hardware sunt permanente si duc de cele mai multe ori la indisponibilizarea circuitului respectiv. B) software: sunt acele erori care duc la alterarea continutului unei locatii de memorie si de cele mai multe ori sunt temporare. FIGURA! Datele citite de pe magistrala sunt convertite intr-un cod (numit si cheie de control) prin intermediul unui circuit de codificare notat f. Atat cuvantul de cod cat si cuvantul citit sunt stocate in memorie. Daca un cuvant avea Mbiti iar codul produce Kbiti in memorie va fi stocat un cuvant de M+Kbiti. Cand datele trebuie furnizate sistemului, cuvantul este citit din memorie impreuna cu cheia de control. Aceeasi functie f este aplicata cuvintelor de Mbiti citite din memorie. Rezultatul fiind comparat cu cheia de control citita din memorie, comparatie care poate genera 3 rezultate: a) nu s-a detectat nici o eroare, ambele chei sunt identice; b) s-au detectat erori dar acestea pot fi corectate; c) s-au detectat erori dar acestea nu pot fi corectate si atunci e activat semnalul de eroare. FIG. 3.15

Preview document

Conținut arhivă zip

- SMP.doc