Extras din laborator

LUCRAREA 1

CIRCUITUL Z - 80 PIO (PARALLEL INPUT OUTPUT)

1. OBIECTUL LUCRĂRII

Lucrarea îşi propune studierea circuitului Z-80 PIO, precum şi realizarea de aplicaţii cu

acest circuit.

2. BREVIAR TEORETIC

Circuitul PIO-Z80 face parte din familia circuitelor I/O ale microprocesorului Z-80 şi este

destinat conectării echipamentelor periferice cu interfeţe paralele, la unităţi centrale realizate cu

microprocesoare Z-80. Pe de altă parte, el asigură generarea şi preluarea de semnale digitale

către şi din exteriorul microsistemului. În acest sens, circuitul Z-80 PIO prezintă două porturi

I/O (regiştri de tip paralel) de câte 8 biţi fiecare, concepute să lucreze independent:

portul A - care poate fi programat în 4 moduri de lucru;

portul B - care poate fi programat în 3 moduri de lucru.

Fiecare port are asociate două semnale, READY şi STROBE, ce pot fi folosite pentru a

asigura controlul unui protocol pentru transferul datelor către şi de la portul paralel (transfer de

tip handshaking).

Cele 4 moduri de lucru sunt:

a) Modul 0 - definit ca ieşire pe octet;

b) Modul 1 - definit ca intrare pe octet;

c) Modul 2 - definit ca intrare / ieşire pe octet;

d) Modul 3 - definit ca intrare / ieşire pe bit.

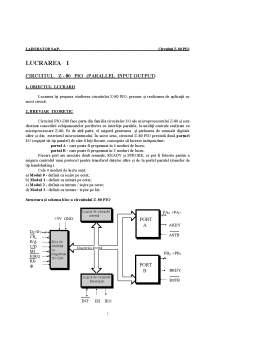

Structura şi schema bloc a circuitului Z-80 PIO

+5V GND

Bloc de

interfaţă

cu

magistrala

UC-Z80

Logică de comandă

internă

Logică de comandă

întreruperi

PORT

A

Magistrala internă

D0÷D7

CS

B/A

C/D

M1

IORQ

RD

Φ

INT IEI IEO

PORT

B

PA0 ÷PA7

ARDY

ASTB

PB0 ÷PB7

BRDY

BSTB

LABORATOR S.uP. Circuitul Z-80 PIO

2

Descrierea conexiunilor externe

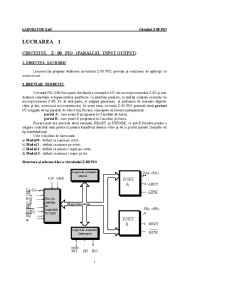

Circuitul Z-80 PIO este realizat într-o capsulă cu 40 pini (conexiuni externe), fiind

alimentat de la o singură sursă de +5V (rămân activi 38 pini).

Circuitul ocupă 4 adrese în spaţiul adreselor de I/O ale microprocesorului, câte două

pentru fiecare port (o adresă de comenzi şi o adresă de date). Circuitul se poate conecta direct la

magistralele unui microsistem cu microprocesor Z-80, fără a mai fi necesară o logică

suplimentară.

Semnalele circuitului se pot grupa în:

- semnale pentru conectarea la magistralele microsistemului;

- liniile magistralei de date;

- semnalele de comandă;

- semnalele pentru logică de întreruperi;

- semnale acesibile utilizatorului;

- liniile portului A;

- liniile portului B.

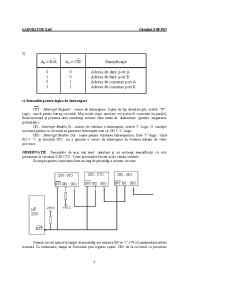

a) Liniile magistralei de date

D0 ÷ D7 - Data Bus. Sunt linii cu caracter bidirecţional (informaţiile se pot transmite pe

aceste linii în ambele sensuri - către şi de la microprocesor). Etajele de ieşire ale acestor linii sunt

prevăzute cu bufferi three-state, ce permit cuplarea la magistrala de date. Prin intermediul

magistralei de date se realizează transferul datelor şi comenzilor între UC (μP ) şi Z-80 PIO.

b) Semnalele de comanda a circuitului

CS - Chip Select. Intrare activă pe ‘0’-logic, ce provine de la o logică de decodificare şi

selecţie, proiectată astfel încât să activeze acest semnal pentru cele patru adrese valide ale

circuitului. În blocul de decodificare intervin semnale din magistrala de adrese (ocmps-ul

acesteia, de regula liniile A2 ÷ A7 ).

M1 - Machine Cycle One - primul ciclu-maşină. Intrare activă pe ‘0’-logic, care provine

de la ieşirea cu acelaşi nume a UC-ului Z-80 (μP). Acest semnal este folosit pentru a realiza

sincronizarea în funcţionare între microprocesor şi circuitul Z-80 PIO.

Circuitul nu dispune de semnal de tip RESET hardware. De aceea, proiectanţii au dotat

această intrare (M1), cu posibilitatea acceptării iniţializarii circuitului. Astfel, o activare a acestei

intrări neînsoţită de activarea semnalelor RD sau IORQ este “înţeleasă” de circuitul PIO ca

reprezentând o iniţializare hardware.

Preview document

Conținut arhivă zip

- Circuitul Z - 80 PIO.pdf