Extras din laborator

Tema proiect:

PROIECTAREA UNITATII DE CONTROL MICROPROGRAMATE

AFERENTA UNUI PROCESOR CISC

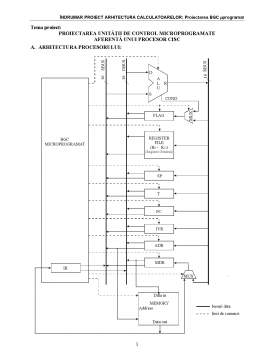

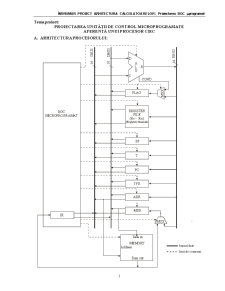

A. ARHITECTURA PROCESORULUI:

SBUS – busul operandului sursa

DBUS – busul operandului destinatie

RBUS – busul rezultatului

FLAG – registrul de flag-uri: N, Z, V, C

REGISTER FILE – file de registre generale (16 registre×16 biti notate R0¸R15); R15 este SP – stack pointer

SP – stack pointer (registrul pointer de stiva)

T – registru tampon (pentru memorari temporare – invizibil programatorului)

PC – program counter (instruction pointer).

IVR – interrupt vector register (registrul vectorului de întrerupere)

ADR – address register (registrul de adrese); are rolul de a adresa locatiile de memorie

MDR – memory data register (registru de date aferent memoriei); furnizeaza datele de scris în memorie în ciclurile de scriere si respectiv este încarcat cu datele citite din memorie în ciclurile de citire

IR – instruction register (registrul instructiunii)

B. FORMATUL INSTRUCTIUNII

Setul de instructiuni este format din patru clase de instructiuni:

b1) instructiuni cu doi operanzi

Cei doi operanzi sunt denumiti operand sursa si respectiv operand destinatie. Pentru localizarea lor se vor defini patru moduri de adresare: imediat, registru direct, registru indirect si indexat. În functie de modul de adresare operandul (sursa sau destinatie) se poate afla într-un registru general sau într-o locatie de memorie. Setul de instructiuni este perfect ortogonal, permitând orice combinatie în ceea ce priveste localizarea celor doi operanzi:

Localizare operand sursa Localizare operand destinatie

registru

registru

memorie

memorie registru

memorie

registru

memorie

Formatul instructiunii cu doi operanzi este:

OPCODE – opcode-ul instructiunii (codul operatiei)

MAS/MAD – mod adresare (operand) sursa/destinatie

RS/RD – registrul (general utilizat pentru adresarea operandului) sursa/destinatie

În cazul acestor instructiuni rezultatul se depune peste operandul destinatie care se va pierde.

În aceasta clasa se definesc urmatoarele instructiuni:

- instructiuni de transfer:

MOV dest, src ;op. dest. ¬ op. src

;op. dest.=operand destinatie

;op. src.=operand sursa

Exemple:

MOV R0,R1 ;R0 ¬ R1

MOV R4,(R2) ;R4 ¬ locatia de memorie adresata de R2

MOV (R3), 124(R5) ;locatia de memorie adresata de R3 ¬ locatia de memorie

;adresata de R5+124; 124 va fi indexul (adresare indexata)

- instructiuni aritmetice:

ADD dest, src ; op. dest. ¬ op. dest. + op. src.

SUB dest, src ; op. dest. ¬ op. dest. - op. src.

Exemple:

ADD (R6),R0 ; locatia de memorie adresata de R6 ¬ locatia de memorie

; adresata de R6 + R0

SUB R3,R5 ; R3 ¬ R3 – R5

- instructiuni logice:

CMP dest, src ; op. dest. – op. src. (fara depunerea rezultatului ci doar

; pentru pozitionarea flag-urilor de conditii)

AND dest, src ; op.dest. ¬ op.dest AND op.src.

OR dest, src ; op.dest. ¬ op.dest OR op.src.

XOR dest, src ; op.dest. ¬ op.dest XOR op.src.

Exemple:

CMP R0,(R1) ; R0 – locatia de memorie adresata de R1 cu pozitionarea

; flag-urilor de conditii conform cu rezultatul scaderii

AND R2,R4 ; R2 ¬ R2 AND R4

OR R1,(R5) ; R1 ¬ R1 OR locatia de memorie adresata de R5

XOR R3,R0 ; R3 ¬ R3 XOR R0

Preview document

Conținut arhivă zip

- Indrumar de Proiect - Arhitectura Calculatoarelor.doc