Cuprins

- 1. Enunțul temei proiectului 3

- 1.2 Prototiparea circuitelor pe placa Terasic / Altera 3

- 2. Descrierea detaliata a aplicației 4

- 2.1 Schema din Deeds-DcS 4

- 2.2 Implementarea fizică a proiectului 5

- 2.3 Lansarea Quartus® II 7

- 2.4 Implementare pe placa DE2-115 10

- 3. Simulare si Rezultat 12

Extras din proiect

1. Enunțul temei proiectului

1.2 Prototiparea circuitelor pe placa Terasic / Altera

In aceasta proiect vom examina măsurile necesare pentru punerea în aplicare a unui circuit pe un Terasic / Altera DE2 bord FPGA. Ținta este de a implementa un prototipe fizic al proiectului și de a testa comportamentul acestuia.

Placa Terasic / Altera DE2 este concepută pentru implementarea practică a circuitelor de semnal digital și mixt, chiar și destul de complexe. Include mai multe dispozitive I/O și interfețe, de la cele simple (switch-uri, butoane, LED-uri, afișaje cu șapte segmente) la dispozitive complexe (afișaj matricial LCD, interfață de rețea Ethernet, USB 2.0, carduri de memorie SD, I/O audio analogic, analogic intrare video, ieșire video VGA și altele ). Miezul DE2 este un FPGA ("Field Programmable Gate Array"), Intel / Altera Cyclone® II 2C35, compus din peste 30.000 de elemente logice (LE). DE2 poate găzdui proiecte introductive simple, precum cel pe care îl prezentăm aici, și proiecte sofisticate care pot include unul sau mai multe microcomputere. .

Pentru a ne concentra asupra metodei de implementare a prototipului, să folosim, ca exemplu de lucru, un circuit foarte simplu . Ne imaginăm că acest circuit va fi rezultatul activităților noastre de proiect și că toate specificațiile de configurare au fost verificate funcțional , utilizând simulare interactivă (și / sau temporizare).

2. Descrierea detaliata a aplicației

Circuit convertor de cod simplu pe 8 biți , de la codul binar natural la codul Gri

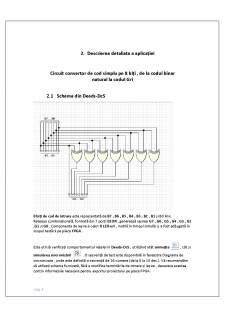

2.1 Schema din Deeds-DcS

8 biți de cod de intrare este reprezentată de B7 , B6 , B5 , B4 , B3 , B2 , B1 și B0 linii.

Rețeaua combinațională, formată din 7 porți EXOR , generează ieșirea G7 , G6 , G5 , G4 , G3 , G2 ,G1 și G0 . Componenta de ieșire a celor 8 LED-uri , inutilă în timpul simulării, a fost adăugată în scopul testării pe placa FPGA .

Este util să verificați comportamentul rețelei în Deeds-DcS , utilizând atât animația , cât și simularea sincronizării . O secvență de test este disponibilă în fereastra Diagrama de sincronizare , unde este definită o secvență de 16 numere (de la 0 la 15 dec.). Vă recomandăm să utilizați schema furnizată, fără a modifica terminările de intrare și ieșire , deoarece acestea conțin informațiile necesare pentru exportul proiectului pe placa FPGA.

Preview document

Conținut arhivă zip

- Circuit convertor de cod simplu pe 8 biti.docx