Cuprins

- Enunţul proiectului . . 4

- Introducere în circuitele logice combinaţionale.5

- Tabelul de adevăr . 6

- Formele canonice disjunctive şi conjunctive ale funcţiilor.7

- Formele minime disjunctive şi conjunctive prin metoda diagramelor Karnaugh. 8

- Minimizarea funcţiilor F1 şi F2 prin metoda Quine-McCluskey .11

- Implementarea funcţiilor logice individuale cu porţi ŞI-NU TTL .14

- Implementarea F1 cu porţi logice ŞI-NU.15

- Implementarea F2 cu porţi logice ŞI-NU.16

- Implementarea F1 cu porţi logice ŞI-NU.17

- Implementarea F1 cu porţi logice ŞI-NU.18

- Implementarea ansamblului cu porţi SI-NU TTL . . 19

- Implementarea ansamblului cu porţi SAU-NU CMOS si ŞI-NU TTL. 21

- Implementare cu MUX-uri în tehnologie CMOS . 24

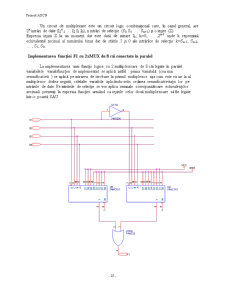

- Implementarea funcţiei F1 cu 2xMUX de 8 căi conectate în paralel.24

- Implementarea funcţiei F2 cu MUX de 8 căi şi o variabilă aplicată pe intrările de date.26

- Implementarea funcţiei F3 cu MUX de 16 căi.28

- Implementare cu DMUX-uri în tehnologie TTL . 29

- Implementarea lui F1 cu DMUX-uri de 8 căi conectate în paralel.29

- Implementarea funcţiei F2 cu DMUX 8 căi şi reţea de porţi logice.31

- Implementare F2 cu DMUX 16 căi şi porţi logice ŞI-NU.34

- Implementarea primei funcţii logice F1 cu DMUX de 16 căi şi porti ŞI.35

- Date de catalog ale circuitelor integrate folosite la implementări . 38

- Calculul timpilor de propagare . 38

- Calcului puterilor disipate . 40

- Concluzii finale . 40

- Bibliografie. 41

Extras din proiect

Enunţul proiectului nr. 77

Să se proiecteze un convertor de cod de 4 biţi pentru conversia codului binar zecimal ponderat 7421 în codul binar zecimal ponderat 5421 (logică combinaţională).Proiectul va cuprinde următoarele puncte:

a) Să se exprime funcţiile logice asociate circuitului combinaţional cu FCD (forma canonică disjunctivă), FCC (forma canonică conjunctivă) tabel de adevăr şi di-agrame Karnaugh.

b) Să se obţină formele minime disjunctive şi conjunctive pentru funcţiile logice asociate convertorului de cod, (utilizând combinaţiile indiferente) prin metoda diagramelor Karnaugh; de asemenea se vor obţine formele minime disjunctive pentru primele două funcţii logice de ieşire şi prin metoda Quine-McCluskey.

c) Să se implementeze fiecare funcţie, independent, numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

d) Să se implementeze ansamblul funcţiilor logice numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

e) Să se implementeze ansamblul funcţiilor logice în următoarea variantă: primele două funcţii logice de ieşire cu porţi logice SAU-NU, realizate în tehnologia CMOS, iar următoarele două cu porţi logice ŞI-NU, realizate în tehnologia TTL.

f) Să se implementeze ansamblul funcţiilor logice cu MUX-uri de 8 respectiv 16 căi (circuitele sunt realizate în tehnologia CMOS).

g) Să se implementeze ansamblul funcţiilor logice cu DMUX-uri de 8 respectiv 16 căi şi porţi logice ŞI-NU în prima variantă, respectiv ŞI în a doua variantă (toate circuitele sunt realizate în tehnologia TTL).

h)Să se calculeze timpii de propagare „intrare-ieşire”, pentru toate schemele logice obţinute.

i) Să se calculeze puterile disipate pentru toate schemele logice obţinute.

j) Să se compare soluţiile de implementare obţinute.

k) Se va face analiza, prin simulare, a tuturor schemelor logice obţinute utilizându-se pachetul de programe OrCAD.

Pe schemele logice obţinute se vor specifica tipul şi gradul de utilizare al fiecărui circuit integrat.

Introducere

Un circuit logic combinaţional este un circuit de comutare combinaţională ce se caracterizează prin aceea că la un moment dat starea ieşirilor circuitului depinde doar de starea intrărilor sale. Legătura dintre starea ieşirilor şi starea intrărilor este dată şi în acest caz de funcţia de transfer a circuitului.

Suportul fizic utilizat în CLC este destul de variat. Studiul CLC şi al celor secvenţiale se face folosind un model al acestora numit reţea de comutare sau schemă logică. În reţeaua de comutare sau schema logică se face abstracţie de caracteristicile constructive ale elementelor ce concep reţeaua sau schema logică avându-se în vedere doar proprietăţile lor funcţionale. Din acest motiv reţeaua are un înalt grad de generalitate, permiţând studiul unor clase largi de circuite logice.

Schema bloc generală (modelul general) al unui CLC reprezentat printr-o reţea de comutare sau schemă logică este următorul:

X1, X2, …,Xn – setul valorilor de intrare

Z1, Z2, …, Zm – setul valorilor de iesire

Relaţii generale între aceste valori:

f(X1, …,Xn) fi – funcţii logice

Z1 = ……………. Xi – variabile logice

Zm = f(X1, …,Xn)

Analiza circuitelor logice combinaţionale

Prin analiza unui CLC se înţelege obţinerea expresiilor mărimilor de ieşire cunoscându-se setul variabilelor de intrare si configuraţia reţelei. Înţelegem numărul şi tipul de elemente logice care intră în componentă ,modul de conectare, punctul în care se aplică variabilele de intrare, numărul de nivele logice etc.

Analiza reţelelor CLC realizate cu elemente logice de tip inversor (ŞI-NU, SAU-NU): numărul maxim de elemente logice aflate între intrarea şi ieşirea reţelei determinã numărul de nivele logice ale acestuia. Numerotarea lor se face de la ieşire către intrare. Într-o reţea de comutare realizate cu elemente ŞI-NU respectiv SAU-NU s-a observat cã o variabilã de intrare apare negată în expresia ieşirii în cazul în care a parcurs un număr impar de elemente de inversare si necomplementată dacă a parcurs un număr par de astfel de elemente.

Tabelul de adevăr

În codul 7421 deosebirea faţa de codul binar natural constă în faptul că secventa binară de cifre 1000 este omisă continuându-se cu următoarea secvenţă.

Codul 5421 are caracteristica următoare: cifrele de la 5 la 9 se deosebesc de cifrele de la 0 la 4 numai prin primul bit ( 0 pentru intervalul 0-4 respectiv 1 pentru intervalul 5-9).

Preview document

Conținut arhivă zip

- Convertor de Cod de 4 Biti pentru Conversia Codului Binar Zecimal Ponderat 7421 in Codul Binar Zecimal Ponderat 5421 (Logica Combinationala).doc