Extras din proiect

Abstract: The project is to use VHDL and FPGA to design an digital clock that has digital display. Basically, the design can display minutes and second. Refer to the traditional watches, the design has stopwatch function and can also memorate split timing.

1. Scopul lucrarii

Se cere proiectarea unui multipol logic care sa permita afisarea timpului – minute secunde - pe afisajul cu afisoare 7 -segmente al placii SPARTAN 3.Acesta va indeplini functiile unui cronometru si pentru aceasta se cere memorarea anumitor timpi,memorare ce are loc la comanda utilizatorului cronometrului.De asemenea,tot in funtie de comanda utilizatorului,se poate trece de la afisarea normala a functionarii ceasului la afisarea timpilor retinuti in memorie. Pentru afisare se va folosi blocul de afisare multiplexata.

2.Desfasurarea lucrarii

Aplicatia “Cronometru digital” se bazeaza pe divizoare de frecventa,numaratoare,blocuri de memorare si afisare.Pentru realizarea aplicatie am folosit

softul Xilinx ISE 10.1 si Modelsim XE III 6.3 C,cel din urma avand rol de simulator.

Schema aplicatiei(realizata in Xilinx) este impartita in patru blocuri:

- Blocul keys:are rolul de a controla lucrul cu intrarile schemei,intrari ce vor fi legate la butoanele placii SPARTAN3;

- Blocul timer:se ocupa cu functionarea efectiva a ceasului cronumetrului,fiind compus din mai multe counter-e;

- Blocul memory:se ocupa cu retinerea timpilor la comanda utilizatorului,avand in componenta un bloc de memorie;

- Blocul display:este un bloc ce realizeaza o afisare multiplexata,fie a ceasului cronometrului fie a timpilor retinuti in memorie.

Astfel schema aplicatie este urmatoarea:

Figura 1 Schema generala a cronometrului digital

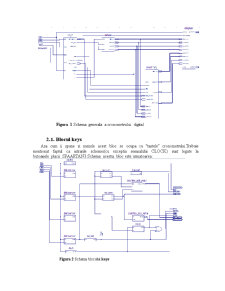

2.1. Blocul keys

Asa cum ii spune si numele acest bloc se ocupa cu “tastele” cronometrului.Trebuie mentionat faptul ca intrarile schemei(cu exceptia semnalului CLOCK) sunt legate la butoanele placii SPAARTAN3.Schema acestui bloc este urmatoarea:

Figura 2 Schema blocului keys

2.1.1 Intrarile schemei cronometrului

In cadrul implementarii aplicatiei pe placa SPARTAN3 intrarile schemei aplicatiei vor fi legate la butoanele placii.Intrarile schemei sunt:

-butonul start:la o simpla apasare a butonului(care inseamna trecerea intrarii din starea LOW in starea HIGH si apoi intoarcerea in starea LOW) cronometrul este pornit,la urmatoarea apasare este oprit,la urmatoarea este pornit din nou si asa mai departe;

-butonul reset: la o simpla apasare a butonului(trecerea LOW-HIGH-LOW) cronometrul este resetat;

-butonul save:orice apasare a acestui buton duce la salvarea in memorie a timpului indicat de cronometru la momentul apasarii;

-butonul mem:apasarea sa duce la trecerea de la afisarea ceasului conometrului la afisarea timpilor salvati in memorie(in acest caz butoanele start si reset vor avea functii de up si down pentru a selecta timpii salvati in memorie,pe care dorim sa-i afisam).O noua apasare a buonului duce la reafisarea normala a cesului cronometrului si implicit butoanele start si reset isi vor indeplini vechiile functii de baza;

-intrarea clk:reprezinta semnalul CLOCK al aplicatiei si se leaga la ceasul placii SPARTAN3,semnal ce are o frecventa de 50 MHz.

Figura 3 Intrarile cronometrului

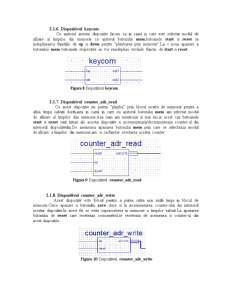

2.1.2. Dispozitivul div50

In primul rand va fi necesar un divizor de frecventa care va activa un semnal din 50 de milioane in 50 de milioane de impulsuri de ceas, deoarece frecventa oscilatorului local este de 50 MHz. Acest semnal se va numi div50 (clock enable seconds) si va valida numaratoarele de la blocul timer al cronometrului.

Figura 4 Dispozitiv div50-divizor de frecventa

Deoarece simularea proiectului care include un astfel de divizor ar dura foarte mult, valoarea finala din procesul pentru divizor va avea valoarea 8 pentru simulare si 50 000 000 pentru implementare pe placa de test. clk_out-ul divizorului se va activa pentru valoarea 1 a lui outp.

2.1.3. Dispozitivul div5

Este un dispozitiv analog celui anterior,avand tot rolul de divizor de frcventa producand la iesire un semnal de ceas cu frecventa mai mica decat cea a ceasului local.Este folosit spre exemplu la counter-ul de la afisarea multiplexata,acolo unde daca am fi folosit ceasul local,datorita frecventei mari a acestuia(50 MHz) nu am fi reusit afisarea,dispozitivele neputand functioana in conformitate cu counter-ul respectiv si neavand timp sa intre in functiune.

Preview document

Conținut arhivă zip

- Cronometru Digital.doc