Extras din proiect

Sa se proiecteze si sa se implementeze pe o structura reconfigurabila XILINX Spartan 3 XC35400 un circuit logic cu urmatoarele caracteristici:

-intrare – butoane;

-iesire – port VGA;

-operatie efectuata – SAU exclusiv cu AA Hex.;

-numar operatii – 4;

CAPITOLUL 1.

PROIECTAREA HARDWARE A SISTEMULUI

Notiuni teoretice

Circuitele reconfigurabile de tip FPGA sunt organizate astfel incat sa acopere o arie vasta de aplicatii. Familia Spartan3 foloseste circuite componenete dedicate pe aplicatii astfel:

• Spartan3-E: se caracterizeaza printr-o densitate ridicata a blocurilor logice; sunt ideale in aplicatii in care se cer realizarea de blocuri de procesare a datelor de dimensiuni mari;

• Spartan3-AN: sunt circuite dedicate pentru aplicatii integrate; acestea contin, printre altele, memorii de configuratie nevolatile;

• Spartan3-A: sunt circuite dedicate pentru interfatarea cu numeroase alte dispositive; acestea poseda blocuri IO optimizate pentru lucrul cu semnale diferentiale si interfatari de memorie;

• Spartan3-ADSP: sunt circuite FPGA optimizate pentru procesarea digitala a semanalelor ( DSP);

Un circuit FPGA prezinta urmatoarele resurse:

• memorii block RAM;

• blocuri logice configurabile(configurable logic block - CLB): reprezinta componenta de baza prin care pot fii implementate functii logice, dar si functii de stocare. De asemenea, CLB permit efectuarea propagarii transportului intr-un lant aritmetic sau interconectarea cu alte blocuri;

• circuitul administrator al semanlului de ceas(digital clock manager - DCM): asigura generarea semnalelor de ceas necesare pentru efectuarea anumitor operatii secventiale;

• blocuri de inmultire si alte operatii aritmetice(multiplication block - MB): asigura implementarea operatiilor aritmetice de inmultire ;

In familia de circuite Spartan3, exista in fiecare componenta a familiei mai multe blocuri de inmultire a 2 numere pe 18 biti fiecare cu semn.

Familia de circuite Spartan3 a fost proiectata pentru a aduce o capacitate sporita si un cost redus, specifice pietei bunurilor de larg consum. Aceasta familie de circuite are 8 membri cu capacitatii intre 50.000 si 5.000.000.000 de porti logice, conform tabelului prezentat mai jos. Circuitele din aceasta familie sunt realizate in tehnologie 90nm si pot fi implementate cu frecventa de lucru pana la 185 MHz. In proiect vom folosi membrul: XC3S400.

Dispozitiv Nr. total de porti Nr. CLB-uri Mem. RAM distribuita(bit) Mem. RAM in blocuri(bit) Multiplicatoare dedicate DCM-uri Nr. porturi I/O

XC3S50 50K 192 12K 72K 4 2 124

XC3S200 200K 480 30K 216K 12 4 173

XC3S400 400K 896 56K 288K 16 4 264

XC3S1000 1M 1920 120K 432K 24 4 391

XC3S1500 1,5 3328 208K 576K 32 4 487

XC3S2000 2M 5120 320K 720K 40 4 565

XC3S4000 4M 6912 432K 1728K 96 4 712

XC3S5000 5M 8320 520K 1872K 104 4 784

CAPITOLUL 2.

PREZENTAREA CIRCUITULUI

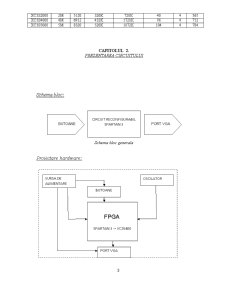

Schema bloc:

Schema bloc generala

Proiectare hardware:

Schema bloc a sistemului cu FPGA

Schema bloc hardware este realizata in jurul unui circuit reconfigurabil FPGA cum este prezentat in figura de mai sus. Prin aceasta se realizeaza comenzile tuturor modulelor component ale schemei.

Preview document

Conținut arhivă zip

- Structuri Hardware Reconfigurabile.doc