Cuprins

- CAP. I INTRODUCERE .

- CAP. II DESCRIERE GENERALĂ .

- 2.1. Arhitectura dispozitivului .

- 2.2 Elementul programabil de interconectare .

- 2.3. Modulele logice .

- 2.4. Memoria încorporată .

- 2.5. Intrări / Iesiri (I/O) logice .

- 2.6 Direcționarea .

- 2.7. Resurse globale .

- 2.8. Modul consum redus de energie (LP) .

- 2.9. Mediul de proiectare .

- 2.10. Programarea .

- 2.11. Capacitățile de diagnosticare și depanare .

- CAP. III NOTE APLICATIVE

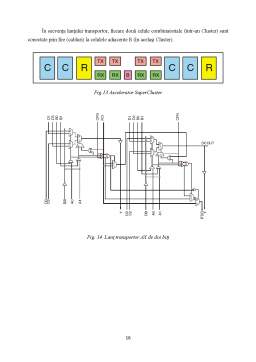

- MACROCOMENZI DE TRANSPORT ALE AXCELERATORULUI .

- 4.1. Introducere .

- 4.2. Celula combinatorială .

- 4.3 Modelul lanţului transportor .

- 4.4 Macrocomenzi ale lanţului transportor .

- 4.5. Performanțe .

- 4.6. Concluzii .

- BIBILIOGRAFIE .

Extras din proiect

CAPITOLUL I

INTRODUCERE

Cea mai recentă familie de elemente FPGA de tip antifuse oferită de Actel, Axcelerator, oferă performanțe ridicate și un design de securitate fără precedent la densități ce depășesc 2 milioane de sisteme de porți echivalente.

În cazul conexiunilor permanente se utilizează elemente de tip “antifuse” (fig.1), cu contact permanent stabilit, ca urmare a aplicării temporare a unei tensiuni ridicate (Actel, QuickLogic, Crosspoint).

Fig.1. Conexiune permanentă cu element de tip “antifuse”.

Ca avantaje se pot menţiona: caracterul nevolatil, dimensiunile relativ mici, rezistenţa şi capacitatea reduse, iar ca dezavantaje: conţinutul fix, imposibilitatea reprogramării etc.

O serie de detalii de implementare pentru conexiunile permanente realizate cu ajutorul unor fuzibile (“fuse”) sunt date în figura 2.

Fig. 2 Detalii pentru conexiunile permanente realizate cu ajutorul fuzibilelor

Dispozitivele Axcelerator ce utilizează arhitectura Actel AX, conțin mai multe nivele – sistem de funcții cu memorii integrate de tip SRAM, PLL, ceasuri segmentabile, cipuri și posibilitatea efectuării oprațiilor logice. Dispozitivele Axcelerator se bazează pe șapte straturi de metal realizate cu ajutorul tehnologiei CMOS antifuse și oferă un nivel de performanță disponibil numai în tehnologia ASIC.

CAPITOLUL II

DESCRIERE GENERALĂ

2.1. Arhitectura dispozitivului

Arhitectura AX derivata din sucesul obținut de arhitectura SX, a fost concepută pentru performanțe ridicate și o utilizare totală a modulului logic (fig.3). Spre deosebire de tradiționalele FPGA, un întreg nivel al dispozitivelor Axcelerator este acoperit cu o grilă de module logice, cu cip virtual ce se pierde in zona de interconectare a elementelor sau la rutare.

Fig.3

2.2 Elementul programabil de interconectare

Familia Axcelerator folosește un element interconectat programabil metal la metal, care se află între cele două straturi superioare de metal (figura 4). Acest lucru elimină complet canalele de direcționare (rutare) și resursele de interconectare dintre modulele logice (puse în aplicare pe tradiționalele FPGA) și permite folosirea eficientă a mai multor module de arhitecturi. Un antifuse este un circuti deschis și când este programat, are o formă permanentă, pasivă, o impedanță de conexiune joasă, duce la propagarea rapidă a semnalului în industrie. În plus datorită mărimii extrem de scăzute a elementulelor de interconectare, familia Axcelerator dispune de resurse importante pentru de direcționare.

Preview document

Conținut arhivă zip

- Actel, Circuite FPGA (Antifuse), Familia - Axcelerator.docx