Extras din proiect

Enunţul proiectului nr.10

Un circuit logic combinaţional este definit de următoatele funcţii booleene:

1. Să se exprime funcţiile , şi cu FCND( forma canonică nominală disjunctiva), FCNC (forma canonică nominală conjunctivă), tabel de adevăr şi diagramă Karnaugh.

2. Să se obţină formele minime disjunctive şi conjunctive ale funcţiilor utilizând metoda diagramelor Karnaugh.

3. Să se obţină forma minimă disjunctivă a funcţiei cu metoda Quine-McCluskey.

4. Să se implementeze ansamblul de funcţii logice utilizând numai porţi logice Şi-Nu realizate în tehnologia TTL.

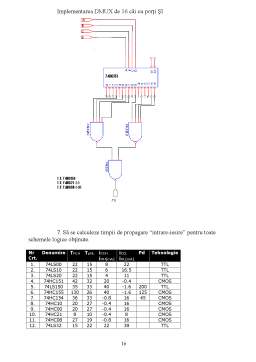

5. Să se implementeze ansamblul de funcţii logice cu MUX-uri de 8 şi respectiv 16 căi realizate în tehnologia TTL.

6. Să se implementeze ansamblul de funcţii logice cu DMUX-uri de 8 şi respectiv 16 căi şi porţi logice Şi-Nu în primă variantă, respectiv Şi în varianta a doua, toate realizate în tehnologia CMOS.

7. Să se calculeze timpii de propagare “intrare-iesire” pentru toate schemele logice obţinute.

8. Să se calculeze puterile disipate pentru toate schemele logice obţinute.

9. Să se compare solutiile de implementare obţinute.

10. Se va face analiza, prin simulare, a tuturor schemelor logice obţinute utilizându-se pachetul de programe OrCAD.

Pe schemele logice obţinute se vor specifica tipul şi gradul de utilizare al fiecărui circuit integrat.

Un circuit logic combinaţional este un circuit de comutare combinaţională ce se caracterizează prin aceea că la un moment dat starea ieşirilor circuitului depinde doar de starea intrărilor sale. Legătura dintre starea ieşirilor şi starea intrărilor este dată şi în acest caz de funcţia de transfer a circuitului.

Suportul fizic utilizat în CLC este destul de variat. Studiul CLC şi al celor secvenţiale se face folosind un model al acestora numit reţea de comutare sau schemă logică. În reţeaua de comutare sau schema logică se face abstracţie de caracteristicile constructive ale elementelor ce concep reţeaua sau schema logică avându-se în vedere doar proprietăţile lor funcţionale. Din acest motiv reţeaua are un înalt grad de generalitate, permiţând studiul unor clase largi de circuite logice.

Schema bloc generală (modelul general) al unui CLC reprezentat printr-o reţea de comutare sau schemă logică este următorul:

Prin analiza unui CLC se înţelege obţinerea expresiilor mărimilor de ieşire cunoscându-se setul variabilelor de intrare si configuraţia reţelei. Înţelegem numărul şi tipul de elemente logice care intră în componentă ,modul de conectare, punctul în care se aplică variabilele de intrare, numărul de nivele logice etc.

Un element SI-NU/SAU-NU realizeaza operaţia sau/şi asupra variabilelor de intrare complementate dacă se afla pe un nivel de inversare impar, respectiv sau/şi asupra variabilelor intrare necomplementate dacă se află pe un nivel de inversare par.

Sinteza schemelor logice combinaţionale are ca finalitate obţinerea efectivă a circuitelor combinaţionale folosindu-se operatori logici care satisfac condiţiile unui sistem de funcţii complet şi pornind de regule de la forma canonică disjunctivă sau conjunctivă.

Preview document

Conținut arhivă zip

- Circuit Logic Combinational.doc