Extras din proiect

Un circuit logic combinaţional este definit prin următoarele funcţii logice booleene:

;

;

.

Se cere:

a) Să se exprime funcţiile f1, f2 şi f3 cu FCC (forma canonică conjunctivă), FCD, tabel de adevăr şi diagrame Karnaugh.

b) Să se obţină ambele forme minime (disjunctivă şi conjunctivă) ale funcţiilor logice, utilizându-se metoda diagramelor Karnaugh; se va obţine, de asemenea, forma minimă disjunctivă pentru funcţia f3 şi prin metoda metoda Quine-McCluskey.

c) Să se obţină formele minime disjunctive ale celor trei funcţii logice, folosindu-se metoda minimizării ansamblului.

d) Să se implementeze funcţiile logice, independent, numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

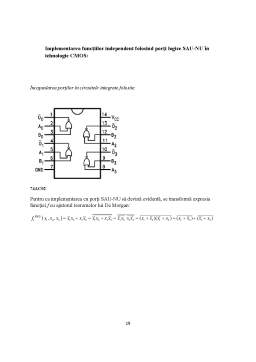

e) Să se implementeze funcţiile logice, independent, numai cu porţi logice SAU-NU (porţile logice sunt realizate în tehnologia CMOS).

f) Să se implementeze ansamblul funcţiilor logice numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

g) Să se implementeze ansamblul funcţiilor logice în următoarea variantă: funcţiile f1 şi f2 cu porţi logice ŞI-NU, realizate în tehnologia TTL, iar funcţia f3 cu porţi logice SAU-NU, realizate în tehnologia CMOS.

h) Să se implementeze ansamblul funcţiilor logice cu MUX-uri de 8 respectiv 16 căi (circuitele sunt realizate în tehnologiaTTL).

i) Să se implementeze ansamblul funcţiilor logice cu DMUX-uri de 8 respectiv 16 căi şi porţi logice ŞI-NU în prima variantă, respectiv ŞI în a doua variantă (toate circuitele sunt realizate în tehnologia CMOS).

j) Să se calculeze timpii de propagare „intrare-ieşire”, pentru toate schemele logice obţinute.

k) Să se calculeze puterile disipate pentru toate schemele logice obţinute.

l) Să se compare soluţiile de implementare obţinute.

m) Se va face analiza, prin simulare, a tuturor schemelor logice obţinute utilizându-se pachetul de programe OrCAD.

Pe schemele logice obţinute se vor specifica tipul şi gradul de utilizare al fiecărui circuit integrat.

Introducere

Circuitele logice combinationale se caracterizeaza prin faptul ca variabilele de iesire sunt independente de timp si de starea interna, fiind determinate numai de variabilele de intrare (starea variabilelor de intrare la momentul considerat).Legatura dintre starea iesirii si starea intrarii unui CLC este realizata de functia de transfer.

Circuitele logice combinationale, CLC, sunt un caz particular al sistemelor secventiale finite sau al automatelor finite, numite automate de grad 0.

Schema bloc generală (modelul general) al unui CLC reprezentat printr-o reţea de comutare sau schemă logică este următorul:

In cadrul analizei CLC se pleaca de la cunoasterea schemei logice a circuitului si se urmareste stabilirea functionarii acestuia. Stabilirea expresiei variabilei de iesire se face de la intrare la iesire, urmarind transformarile variabilelor de intrare.

Pentru reprezentarea unei funcţii booleene se folosesc două forme de bază, numite forme canonice:

• forma produsului de sume, denumită şi forma maxterm (forma canonică conjunctivă - FCC), unde variabilele sau complementarele lor în cadrul unui maxterm sunt legate prin SAU, iar maxtermii între ei sunt legaţi prin ŞI;

• forma sumei de produse, denumită şi forma minterm (forma canonică disjunctivă - FCD), unde variabilele sau complementerele lor în cadrul unui minterm sunt legate prin ŞI, iar mintermii intre ei sunt legaţi prin SAU.

Formele canonice disjunctive ale functiilor

Pentru a obţine din tabelul de adevăr forma canonică conjunctivă se iau în considerare combinaţiile pentru care funcţia are valoarea 0, iar pentru forma canonică disjunctivă se iau în considerare combinaţiile pentru care funcţia are valoarea 1.

Tabelul de adevar

Nr.crt X1X2X3 f1 f2 f3

0 000 0 1 1

1 001 1 0 0

2 010 0 0 1

3 011 1 0 0

4 100 1 1 1

5 101 1 1 1

6 110 1 1 1

7 111 0 1 1

Preview document

Conținut arhivă zip

- Proiect ASDN.doc