Cuprins

- Abstract 3

- 1.Standardul IEEE 1149.1 3

- 1.1.Generalități 3

- 1.2.Controllerul tap 7

- 1.3.Registrul de instructiuni 8

- 1.4.Registrele de date 9

- 1.4.1.Registrul de date Boundary-Scan 10

- 1.4.2.Registrul de date bypass 11

- 1.4.3.Registrul pentru identificarea dispozitivului 11

- 2.Setul de instructiuni IEEE 1149.1 12

- 2.1.Instructiuni obligatorii 12

- 2.1.1.Instructiunea BYPASS 12

- 2.1.2.Instructiunea SAMPLE/PRELOAD 12

- 2.1.3.Instructiunea EXTEST 13

- 2.2.Instructiuni optionale 13

- 2.2.1.Instructiunea INTEST 13

- 2.2.2.Instructiunea RUNBIST 13

- 2.2.3.Instructiunea CLAMP 13

- 2.2.4.Instructiunea HIGH_Z 13

- 2.2.5.Instructiunea ID_CODE 14

- 2.2.6.Instructiunea USER_CODE 14

- 3.Extinderea conceptului boundary-scan la nivel de sistem 14

- 4.Formatul datelor 16

- 4.1.Limbajul de descriere boundary-scan 16

- 4.2.Limbajul de descriere pentru scanare ierarhica 17

- 4.3.Formatul vector serial 17

- 5.Sistem de învățare a principiilor tehnicii Boundary-Scan 21

- 5.1.Introducere 21

- 5.2.Noţiuni generale 22

- 5.3.Reprezentarea şi modificarea plăcilor de circuite imprimate 23

- 5.3.1.Reprezentarea unui Chip 24

- 5.3.2.Semnale şi linii 24

- 5.3.3.Modificarea chipurilor şi plăcilor de circuite imprimate 25

- 5.4.Simularea şi Diagnosticarea Erorilor 25

- 5.4.1.Modul TAP Controller 26

- 5.4.2.Modul comandă 26

- 5.5.Concluzii 27

- Referinţe 28

Extras din referat

Abstract

În următoarele pagini ne propunem să prezentăm câteva din cele mai importante caracteristici ale standardului IEEE 1149.1 Boundary Scan (BS) de testare automată și o concepţie asupra unui sistem de învăţare a sa. Sistemul are la bază ideea reprezentării grafice a unui conţinut mai complicat, studentul având posibilitatea să se ‘joace’ cu sistemul de învăţare. Noţiunile incluse în sistemul de învăţare cuprind: designul/modificarea structurilor Boundary Scan din interiorul chip-ului target; designul/modificarea plăcii target care conţine mai multe chip-uri; cercetarea comenzilor BS precum EXTEST, BYPASS ş.a. ; introducerea şi diagnosticarea erorilor de interconectare ; simularea funcţionării unui controller TAP, a regiştrilor de scanare şi a altor regiştrii BS. Sistemul este implementat sub forma unui program applet Java şi poate fi accesat gratuit pe Internet. Acest lucru uşurează folosirea sistemului de către orice student al oricărei universităţi.

1.Standardul IEEE 1149.1

1.1.Generalități

Standardul IEEE 1149.1 reprezintă un protocol general și o arhitectură specifică, dezvoltate ca rezultat al unei cooperări între aproximativ 200 de firme cu profil electronic. Iniţiatorii acestui standard sunt AT&T , DEC, Ericsson , IBM, Nixdorf, Philips, Siemens și Texas Instruments. Aceste firme au agreat ideea că numai o arhitectură generică, care să nu constituie proprietatea exclusivă a unei singure firme, va încuraja alte companii să producă circuite integrate compatibile, echipamente de test și software CAD într-o idee unitară, care să reducă costurile de dezvoltare, producţie și testare pentru echipamentele electronice. Se crede că arhitectura BS va reprezenta pentru dezvoltarea, producţia și testarea echipamentelor electronice ceea ce reprezintă în momentul de fata standardul RS-232C pentru echipamentele periferice.

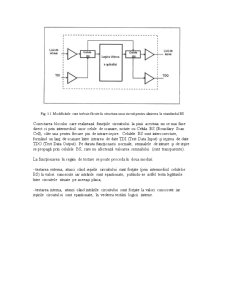

Aşa cum s-a menţionat mai sus, BS reprezintă o particularizare a metodei de scanare la nivelul pinilor de intrare-ieşire ai unui circuit, în scopul adăugării observabilității și controlabilității circuitului. În figura 1.1 se ilustrează modificările care trebuie făcute în structura unui circuit pentru alinierea la standardul BS.

Fig. 1.1 Modificările care trebuie făcute în structura unui circuit pentru alinierea la standardul BS

Conectarea blocului care realizează funcţiile circuitului la pinii acestuia nu se mai face direct ci prin intermediul unor celule de scanare, notate cu Celula BS (Boundary Scan Cell), câte una pentru fiecare pin de intrare-ieşire. Celulele BS sunt interconectate, formând un lanţ de scanare între intrarea de date TDI (Test Data Input) și ieşirea de date TDO (Test Data Output). Pe durata funcţionarii normale, semnalele de intrare și de ieşire se propagă prin celulele BS, care nu afectează valoarea semnalului (sunt transparente).

La funcţionarea în regim de testare se poate proceda în doua moduri:

- testarea externa, atunci când ieşirile circuitului sunt forţate (prin intermediul celulelor BS) la valori cunoscute iar intrările sunt eşantionate, putându-se astfel testa legăturile între circuitele situate pe aceeaşi placa;

- testarea interna, atunci când intrările circuitului sunt forţate la valori cunoscute iar ieşirile circuitului sunt eşantionate, în vederea testării logicii interne.

Preview document

Conținut arhivă zip

- Testare Automata - Standardul IEEE 1149.1 - Boundary Scan.doc