Extras din seminar

Pentru a creste performanta procesoarelor a fost dezvoltata tehnica “benzii de asamblare”, numita si pipeline. Majoritatea procesoarelor din zilele noastre o folosesc datorita simplitatii si eficacitatii. Este folosita in special cu arhitecturile de RISC.

Datorita unor particularitati ale procesarii pipeline (in special hazardurile pe care aceasta le implica), apare necesitatea unor compilatoare optimizate zise si reorganizatoare sau schedulere, cu rolul de a reorganiza programul sursa pentru a putea fi procesat optimal din punct de vedere al timpului de executie.

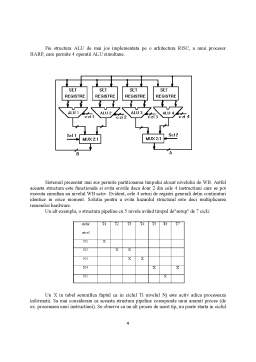

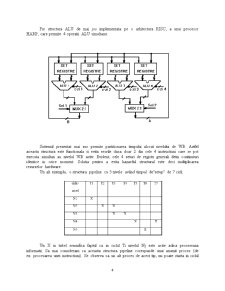

Tehnica pipeline se bazeaza pe principiul urmator: intrucat o instructiune dureaza mai putin decat intreg programul (ca timp de efectuare) putem castiga timp daca reusim sa punem mai multe procesoare sa faca instructiuni diferite, intr-o ordine bine diferita simultan. Pentru un set de 3 instructiuni de exemplu, daca alocam 3 procesoare putem reduce de pana la 3 ori timpul de rulare al unui program, in conditiile in care acesta lucreaza in bucla.

Totusi ne lovim de anumite constrangeri si nu putem executa mai multe instructiuni consecutive chiar una dupa alta, ba mai mult putem ajunge la un blocaj al procesarii, ceea ce reprezinta in primul rand un efect negativ asupra ratei de executie a instructiunilor. Asemenea constrangeri le numim “hazarde”.

Exista 3 tipuri de hazarde:

- Structurale;

- De date;

- Ale controlului sau de ramificatie.

Hazardele structurale

Structura procesorului nu permite executarea anumitor tipuri de instructiuni simultan in stagii diferite.

Ca exemple avem:

- mai multe instructiuni vor sa acceseze simultan acelasi registru din memorie (o instructiune care vrea sa-si adune operanzii, reuseste acest lucru, si o instructiune care a terminat si vrea sa scrie rezultatul -> exista posibilitatea ca rezultatul primei instructiuni sa depinda de cea de a doua si atunci rezultatul va fi gresit);

- avem instructiuni cu numarul de ciclii masina diferit;

- o instructiune foloseste o anumita unitate a procesorului, iar in acelasi timp o alta instructiune ar putea dori sa foloseasca acea unitate -> intarzieri.

O prima solutie ar fi prin multiplicarea unitatilor functionale catre sunt in conflict. Aceasta nu este totusi o solutie fezabila: implica costuri suplimentare in productie. Totodata nu asigura rezultatul dorit (spre exemplu la operatiile in virgula mobila, care pot dura si cateva zeci de ciclii masina, simpla duplicare a unitatii de calcul nu este de ajuns).

O alta solutie, implementata pe procesoarele de generatie mai noua consta in integrarea de bus-uri si cache-uri unificate pe instructiuni si date specifice.

Se foloseste de asemenea ca solutie dezvoltarea software, prin realizarea unor compilatoare care sa ajute partea hardware sa evite situatiile de acest gen prin asa numitul code schedulling. Aceasta se bazeaza prin umplerea spatiului dintre doua astfel de instructiuni cu instructiuni de tip noop. Practic compilatoarele incearca sa aranjeze instructiunile codului in asa fel incat instructiuni care depind una de alta sa fie cat mai departe una de cealalta. Si aceasta solutie se poate totusi dovedi ineficienta intrucat arhitectura interna difera de la o arhitectura la alta, deci ne-ar trebui un compilator diferit de la o masina la alta.

Hazardele de date

Apar cand o instructiune depinde de rezultatele unei instructiuni anterioare in banda. Pot fi la randul lor clasificate in 3 categorii, dependent de ordinea acceselor de citire respectiv scriere, în cadrul instructiunilor:

- RAW (read after write)

- WAR (write after read)

- WAW (write after write)

RAW apare atunci cand o instructiune incearca sa citeasca inainte ca alta sa termine de scris, si informatia din sursa respectiva (registru de exemplu) este importanta pentru efectuarea unui calcul corect. Astfel prima instructiune va trebui sa fie intarziata.

O solutie vine imediat si este de tip software: introducerea de intarzieri prin instructiuni de tip noop. In anumite situatii poate fi rezolvata si hardware fara sa cauzeze stagnari ale fluxului de instructiuni. Aceste tehnici se numesc tehnici forwarding si consta in pasarea anticipata a rezultatului de care are nevoie prima instructiune. Asta permite instructiunii din stagiul de decodificare sa-si continue executia netulburata, fara a fi nevoie sa introducem vreun noop.

WAR apare atunci cand o instructiune scrie un rezultat inainte ca acesta sa fie folosit de instructiune ulterioara. Apare de cele mai multe ori, ca si precedentul datorita diferentelor de timp de efectuare a instructiunilor, in functie de complexitatea lor. O solutie fiabila este introducerea cu ajutorul compilatorului, sau direct in sursa a intarzierilor de tip noop.

Pot aparea totusi si din nerespectarea ordinii de efectuare a instructiunilor.

WAW apare atunci cand o instructine scrie rezultatul inaintea unei instructiuni precedente, rezulta o scriere eronata a datelor. Apar la structurile pipeline care au mai multe nivele de scriere si care permit unei instructiuni sa scrie daca alta a fost blocata. Ca exemplu modurile de adresare indirecta cu postincrementare. Pot fi eliminate prin scheduling cu ajutorul compilatorului.

Hazardele WAR si WAW nu sunt reale, ci mai degraba conflicte de nume si de aceea se mai numesc dependente de iesire sau antidependente. Solutia pentru ele fiind organizarea pasilor programului sau impunerea unei relatii de precedenta.

Preview document

Conținut arhivă zip

- Tema 8 - Hazarde Structurale la Procesoarele de Tip Pipeline - Exemple Reale si Solutii.doc